# 一种含噪声测试的数字化电能表计量性能检测系统\*

徐宏伟<sup>1</sup> 魏伟<sup>2</sup> 张秋雁<sup>1</sup> 陈建国<sup>1</sup> 李红斌<sup>3</sup>

(1. 贵州电网有限责任公司电力科学研究院 贵阳 550000; 2. 国网湖北省电力公司计量中心 武汉 430080;

3. 华中科技大学电气学院 武汉 430074)

**摘要:**电子式互感器属于电子设备,在A/D采样过程中不可避免的会产生噪声,噪声叠加至采样值中,对电能计量的准确性产生明显影响,有必要对数字化电能表入网运行前展开输入噪声测试,保证数字化电能表入网运行的准确性。因此,研究了一种含噪声测试的数字化电能表计量性能检测系统,检测系统在现有数字化电能表检测项目的基础上,提出了输入噪声测试项目及测试方法,通过研究发现,数字化电能表在噪声条件下误差明显增大及不稳定,当信噪比为30 dB时,数字化电能表误差出现超差现象,建议数字化电能表入网运行前增加输入噪声测试项目。

**关键词:**IEC61850; 数字化电能表; 计量性能; 检测系统; 高斯白噪声

中图分类号: TN98 文献标识码: A 国家标准学科分类代码: 470.40

## A metering performance testing system of digital watt-hour meter with noise testing function

Xu Hongwei<sup>1</sup> Wei Wei<sup>2</sup> Zhang Qiuyan<sup>1</sup> Chen Jian'guo<sup>1</sup> Li Hongbin<sup>3</sup>

(1. Electric Power Research Institute of Guizhou Power Grid Co., Guiyang 550000, China;

2. Mesurement Center, State Grid Hubei Electric Power Company, Wuhan 430080, China;

3. Huazhong University of Science and Technology, Wuhan 430074, China)

**Abstract:** As an electronic equipment, the merging unit will produce noise in the process of A/D sampling, the noise superposition to sampling value will be obvious influence the accuracy of electric energy metering, it is necessary to do noise testing for digital watt-hour meter before running, and ensure the accuracy of the digital watt-hour meter. Therefore, this paper studies a kind of metering performance testing system of digital watt-hour meter with noise testing function, proposed input noise test items and test method on the basis of existing digital watt-hour meter test items, through the study found that the error of digital watt-hour meter will be increased and unstable obviously under the condition of noise, and when SNR is 30 dB, the error exceeding it's tolerance, suggest to increase the input noise testing before the digital watt-hour meter put into operation.

**Keywords:** IEC61850; digital watt-hour meter; metering performance; testing system; white gaussian Noise

## 1 引言

传统电子式电能表的电能计量模块主要由电能计量芯片组成<sup>[1-2]</sup>,电能计量芯片内置A/D采样单元、数字滤波电路、电能计量单元等,在进行电能量计算时,输入电能表的噪声信号会被数字滤波电路滤除,噪声信号对电子式电能表的影响较小,可以忽略。数字化电能表较传统电能表而言,内部采用光模块获取合并单元输出的光信号<sup>[3-4]</sup>,A/D模数转换单元前置于电子式互感器,而电子式互感

器会因受外界环境的干扰或自身电子元器件的影响,在A/D转换过程中不可避免的会产生噪声,电子式互感器国家标准<sup>[5]</sup>中规定了电流互感器输出的最小信噪比为30 dB,也说明了电子式互感器输出采样值中会叠加噪声的事实,信号经电子式互感器到数字化电能表电能计量的整个链路中并未进行滤除处理,输入的噪声会对数字化电能表的计量准确性产生明显影响,有必要对数字化电能表入网运行前展开输入噪声测试,提出输入噪声测试项目及测试方法,保证其入网运行的准确性和可靠性。

收稿日期:2017-02

\*基金项目:中国南方电网公司科技项目(GZ2014-2-0059)资助

目前数字化电能表的相关国家及企业标准中并未规定输入噪声测试项目,文献[6]研究了一种IEC 61850报文发生器,该报文发生器可以用于数字化电能表的基本误差测试,仅能输出理想的正余弦波形信号,不能用于数字化电能表的输入噪声测试,文献[7]在该报文发生器的基础上,研究了一种基于IEC 61850协议的数字化电能表校验装置,该装置除了实现数字化表基本误差测试外,主要是增加了便于装置自身进行溯源的功能,同样没有从数字化电能表与传统电能表的结构差异性着手,去研究影响数字化电能表计量性能的输入噪声测试方法。此外,文献[8-9]均讨论及提出了数字化电能表的校验方法,且主要侧重于数字化电能表的溯源方案研究。总之,目前已有不少文献对数字化电能表性能测试的装置及系统展开了研究,但是现有的研究均侧重于数字化电能表的基本误差测试及溯源方案的研究,而数字化电能表因结构变化而引起的计量误差的研究并不全面,尤其是输入噪声对数字化电能表计量性能的影响及输入噪声测试方法的研究未见报道。因此,为了研究输入噪声对数字化电能表计量性能的影响,实现数字化电能表输入噪声测试,研究了一种含噪声测试的数字化电能表计量性能检测系统,该系统除了能实现现有数字化电能表检测项目的测试外,还提出了一种基于M序列的Box-Muller变换高斯白噪声叠加方法,能真实模拟电子式互感器叠加噪声情况,实现数字化电能表输入噪声测试,并提出了测试方法,为研究数字化电能表输入噪声条件下的计量性能提供了依据。

## 2 系统原理

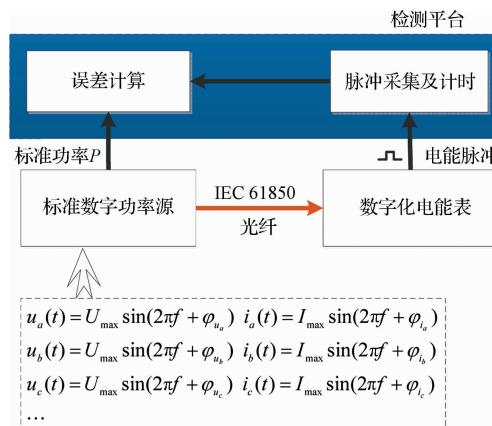

根据检测原理,数字化电能计量性能检测系统的基本组成内容应该包含3个部分:1)标准通道,指为被检数字化电能表提参考标准的部分;2)被校通道,在这里指的是被检数字化电能表;3)检测平台,指进行被检数字化电能表误差计算的部分。研究的检测系统也在这3个组成内容的基础上研制形成,系统原理如图1所示。

如图1所示,检测系统主要由标准数字功率源、被检

图1 检测系统原理

数字化电能表、检测平台组成。研究的检测系统采用瓦秒法对数字化电能表进行误差检测:构建标准数字功率源模拟合并单元输出IEC 61850协议的数据包到被检数字电能表,检测平台利用电能脉冲采集及计时模块采集被检测数字化电能表输出的电能脉冲及时间,并获取标准数字功率源输出的标准功率值P来计算电能量,通过比对标准数字功率源输出的电能量与被检数字化电能表的电能量,即可实现数字化电能表的误差检测。

## 3 系统设计

为实现数字化电能表的检测,系统应除了能满足现有检测项目的要求外,还应该能模拟合并单元输出叠加噪声的采样值报文,这也是该检测系统的关键技术及难点,系统设计主要技术参数如表1所示。

表1 系统主要技术参数

| 序号 | 项 目       | 技术要求         |

|----|-----------|--------------|

| 1  | 报文输出间隔    | 250 μs±10 μs |

| 2  | 谐波设置      | 2~11次谐波      |

| 3  | 频率偏差设置范围  | 48 Hz~52 Hz  |

| 4  | 频率偏差设置分辨率 | 0.1 Hz       |

| 5  | 噪声设置      | 可任意设置        |

如上表所示,标准数字功率源报文输出间隔与合并单元相同,谐波选择常用的2~11次,频率偏差可以在48~52 Hz范围内以0.1 Hz分辨率任意设置,噪声应能按照信噪比任意设置。

### 3.1 标准数字功率源

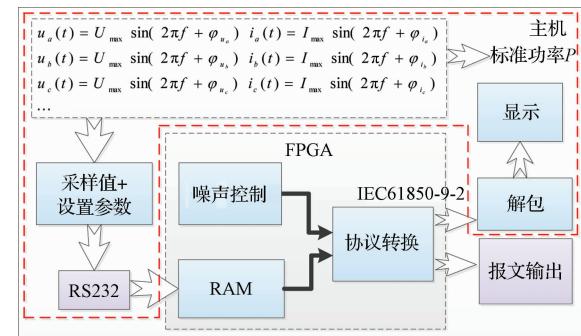

标准数字功率源的研究是该系统组成的关键部分,要求具有高准确度和稳定性,要保证采样数据精度及输出数据严格的时序性。考虑到直接利用工业计算机输出IEC 61850报文时,不能保证其严格的时序性,直接利用微处理器芯片输出IEC 61850报文时,不具备人机交互及波形输出控制功能,选择了工业计算机与实时性高的FPGA相结合的标准数字功率源设计方案,标准数字功率源设计原理如图2所示。

如图2所示,标准数字功率源一方面计算出标准功率

图2 标准数字功率源原理

P 输出给工业计算机内部的误差计算模块;另一方面利用工业计算机的主机设置虚拟负荷波形,并对虚拟负荷波形进行采样,方便用户进行负荷波形及各类参数(如信噪比等)设置,并通过 RS232 通信接口将采样数据点加载到 RAM 中,FPGA 读取 RAM 中采样数据点进行信噪比控制,经协议转换后,通过以太网口和光纤接口输出数据包。下面就具体实现方法进行分析。

### 3.1.1 基础设计

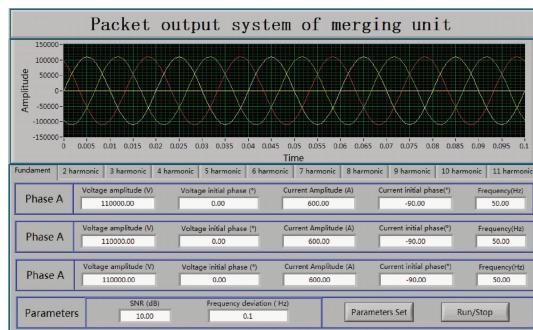

#### 1) 上位机软件设计

为减少 FPGA 工作量,保证报文输出具有严格的时序性及稳定性,检测系统设计了上位机软件用于信号波形的设置,软件选择了人机交互性好的虚拟仪器编程<sup>[10]</sup>,前面板设计图形化用户界面(graphical user interface, GUI),GUI 提供了各类型参数输入,包括基波、谐波的幅值、相位、频率参数、信噪比设置,如图 3 所示。

图 3 图形化用户界面

后面板设计了电流/电压信号函数,信号函数的参数通过前面板的输入进行设置,同时设计信号函数采样模块,采样频率为 4 kHz,选取前 500 个采样点保存到变量存储器。

#### 2) 波形数据加载通信协议设计

采样数据点通过 RS232 串口加载到 FPGA 的 RAM 中进行存储,数据加载过程中容易受到外界的干扰造成数据出现误码现象,造成数字功率源输出波形数据并非所设置的波形,为保证加载过程中数据的纠错与抗干扰能力,系统设计了数据点加载通信协议,只有满足通信协议的数

表 2 数据点加载通信协议

| 序号 | 说 明    | 代 码    |

|----|--------|--------|

| 1  | 帧起始符   | FF 55H |

| 2  | 目标地址   | A0~A5  |

| 3  | 频率偏差   | XX XX  |

| 4  | 信噪比    | XX XX  |

| 5  | 保留位    | XX XX  |

| 6  | 数据起始标志 | F5 F5H |

| 7  | 数据域    | DATA   |

| 8  | 校验码    | CS     |

| 9  | 结束符    | EEH    |

据才能被 FPGA 存储,并进行协议转换输出,通信协议如表 2 所示。

如表 2 所示,所有数据为十六进制表示,目的地址设置为接收报文的目标设备 MAC 地址,频率偏差、信噪比中“XX XX”由上位机程序设置的参数确定,保留位用于对功能的扩展,数据起始标志位标志采样点数据开始,数据域为上位机采样 22 个通道的数据(与目前合并单元普遍采用的通道数相同),每个通道 500 个数据点,校验码为从数据起始标志后第一个数据到校验码之前的所有数据字节模 256 的和,即各字节二进制算术和,不计超过 256 的溢出值,结束符表示通信协议结束。FPGA 接收到上表所示的通信协议报文后,进行帧格式验证,如果帧格式错误,则不保存此次加载的波形数据,反之,则将波形数据保存到 RAM 中。

#### 3) 报文输出设计

报文输出设计是研究的检测系统创新点之一,是为了提高数字功率源输出报文的高效性而设计的,现有的数字功率输出报文时,波形数据采样过程及协议组帧过程均是由 FPGA 或相似的主控芯片完成,由于采样值数据量大,主控芯片在进行采样时容易造成数字功率源报文输出过程中的延时或死机现象,为了解决这一问题,检测系统采样过程前置到上位机程序中,FPGA 仅参与采样值组帧及输出控制,保证了数据包输出严格的时序及稳定性。报文输出过程中 FPGA 以查找表方式读取 RAM 中的采样点,根据上位机设置的参数进行数据报文组帧,并输出 IEC 61850 格式报文。

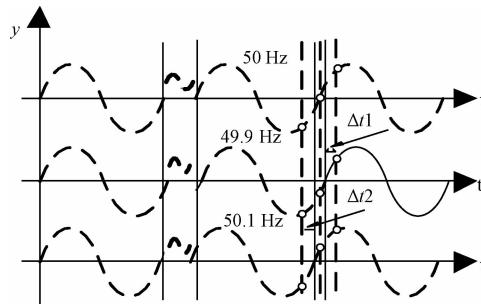

基波、谐波报文输出时,取 RAM 中每个数据通道内 500 个点的前 480 点,即 6 个周波的数据按次序循环进行协议转换输出;频率偏差输出时,取 462~500 个数据点按次序循环进行协议转换输出,实现 52~48 Hz 频率偏差报文输出,每多或少取一个数据点时,频率改变约 0.1 Hz。下面以频率设计为 49.9 Hz 及 50.1 Hz 为例进行说明,当输出频率偏差波形时,输出信号波形如图 4 所示。

图 4 频率偏差报文输出

如图 4 所示,  $\Delta t_1$ 、 $\Delta t_2$  分别为 50 Hz 频率第 6 个整周波与 49.9 Hz、50.1 Hz 波形 6 个整周波之间的时间差,当频率为 49.9 Hz 时,6 个周波的时间为  $t_1 = (1 \times 6) / 49.9 \approx 120.24 \text{ ms}$ 。频率为 50.1 Hz 时,6 个周波的时间为  $t_2 =$

$(1 \times 6)/50.1 \approx 119.76$  ms。由于两个采样点时间间隔为  $T_c = 250 \mu\text{s}$ , 49.9 Hz 频率下, 6 个整周波采样点为  $n1 = t1/T_c = 480.96$ , 因此取最近的整数 481 个波形数据点按次序循环进行协议转换并输出, 此时采样点绝对误差为  $\Delta n1 = 480.96 - 481 = 0.04$ , 转换为时间, 即上图所示的  $\Delta t1 = \Delta n1 \times T_c = 10 \mu\text{s}$ , 平均到 6 个周期, 每个周期误差为  $\Delta t1e = \Delta t1/6 \approx 1.67 \mu\text{s}$ , 转换为频率设计误差:

$$\Delta f1 = \{[49.9/(1 - 1.67 \times 49.9/1\,000\,000) - 49.9]/49.9\} \times 100\% \approx 0.008\%.$$

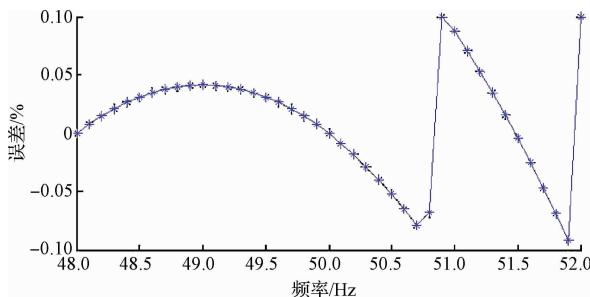

同理得到 50.1 Hz 时取最近的整数 479 个波形数据点输出, 得到频率设计误差为  $\Delta f2 \approx -0.009\%$ 。通过分析发现频率偏差设计在  $\pm 2$  Hz 内变化时, 最大正误差在 50.9 Hz 处为 0.1%, 负误差 50.7 Hz 处为 -0.079%, 频率偏差设计误差分布如图 5 所示。

图 5 频率偏差设计误差分布

### 3.1.2 输入噪声测试功能

电子式互感器及其组件合并单元属于电子设备, A/D 采样过程中不可避免的会产生叠加噪声, 其中主要为热噪声, 热噪声亦称为白噪声, 服从高斯分布, 属于高斯白噪声的一种, 来源是导体内部自由电子无规则的热运行, 当导体接入电路后, 内部波动电势便成为电路的热噪声源, 它与放大器、电阻、电容、半导体等有关, 是固定存在的<sup>[11-12]</sup>, 当合并单元输出报文时热噪声(即高斯白噪声)会叠加到采样值中一同输出。叠加有噪声的采样值会对数字化电能表计量准确性产生严重影响, 研究数字化电能表输入噪声测试方法, 具有重要意义。

考虑到现场噪声条件是随机不定的, 直接利用上位机程序在原始波形数据中添加噪声并加载到 FPGA 的 RAM 中进行循环输出时, 噪声是周期性的, 不足以反应合并单元输出噪声的特征, 因此, 提出了一种基于 M 序列的 Box-Muller 变换高斯白噪声叠加方法, 该方法利用线性反馈移位寄存器(linear feedback shift register, LFSR)设计了 M 序列产生器, 产生(0,1)均匀分布的随机信号, 并通过 Box-Muller 变换将随机信号变换为高斯白噪声信号, 经过信噪比的调整, 即能模拟合并单元输出叠加噪声的数据包, M 序列产生方法如下。

#### 1) M 序列产生电路

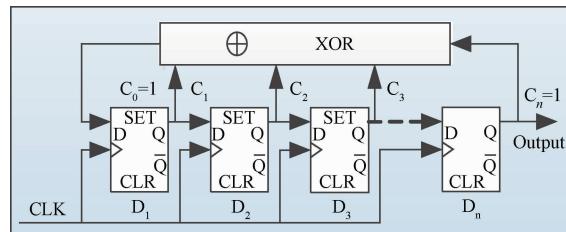

M 序列通常是由带有线性反馈逻辑电路的 LFSR 产

生, 选择了与如图 6 所示的 LFSR 产生 M 序列。图中为  $n$  级移位寄存器( $D_1 \sim D_n$ )构成的 M 序列发生器<sup>[13-14]</sup>,  $C_0 \sim C_n$  均为反馈线,  $C_0 = C_n = 1$  表示反馈连接,  $C_1 \sim C_{n-1}$  若为 1 则表示参与反馈, 反之, 则不参与反馈。输出序列由移位寄存器的级数、初始状态、反馈逻辑和时钟周期共同决定。

图 6 M 序列产生电路

M 序列产生电路的输出最多可以产生  $2^n - 1$  个状态, 即输出数据周期为  $2^n - 1$ , 反馈连接状态见式(1)。M 序列产生电路中 CLK 时钟采用 4 kHz 输入, 为了保证输出数据随机性, 选取了 32 个 D 触发器构成 M 序列发生器, 通过查找 M 序列反馈系统表选取 32 个 D 触发器中的 1, 2, 3, 5, 7, 32 位进行异或得到 M 序列, 输出多项式为:

$$f(x) = 1 + x + x^2 + x^3 + x^5 + x^7 + x^{32} \quad (1)$$

M 序列产生的每一个状态为二进制格式的数据, 通过转换变为十进制数对应一个随机噪声, 由 M 序列产生器的状态变化, 可以得到随机均匀噪声序列, 经过归一化变换为(0,1)上均匀分布的随机噪声信号。M 序列产生电路得到随机噪声信号属于白噪声, 不能直接将产生的噪声信号用于数字化电能表的测试, 需要使噪声信号服从高斯分布, 因此, 本文选取了应用广泛的 Box-Muller 对产生的白噪声信号进行变换, 经过变换后的噪声信号服从高斯分布, 即得到高斯白噪声信号, Box-Muller 变换方法如下。

#### 2) Box-Muller 变换

取  $r_1$  和  $r_2$  为 M 序列中两个相互独立的均匀随机数<sup>[15]</sup>, 则 Box-Muller 变换如下所示:

$$\begin{cases} x_1 = (-2 \ln r_1)^{1/2} \cos(2\pi r_2) \\ x_2 = (-2 \ln r_1)^{1/2} \sin(2\pi r_2) \end{cases} \quad (2)$$

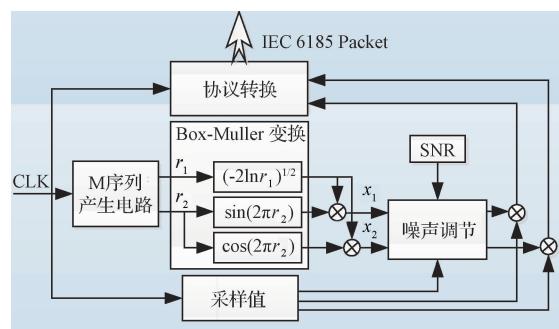

经过上式变换后,  $x_1$ 、 $x_2$  为服从(0,1)分布的高斯白噪声。噪声输出设计总体原理如图 7 所示。

图 7 噪声输出产生原理

图 7 中噪声调节模块能对高斯随机序列的幅值进行调节, 调节完后的序列与波形数据进行叠加, 具体过程如下。

噪声调节模块在读取 RAM 中的波形数据后, 选取波形数据点计算出信号的有效值  $V_s$ :

$$V_s = \sqrt{\frac{1}{n} \sum_{i=0}^n V_{si}^2} \quad (3)$$

式中:  $V_{si}$  为第  $i$  个波形数据点的值,  $n$  为用于计算信号有效值的点数, 此处选取 1 个周波数据点。

得到  $V_s$  后, 噪声调节模块利用信噪比计算公式计算出噪声有效值  $V_n$ :

$$SNR = 20 \lg \frac{V_s}{V_n} \quad (4)$$

取信号波形序列为  $f1(n)$ , Box-Muller 变换后输出的高斯白噪声序列为  $f2(n)$ ,  $f(n)$  为噪声叠加过程后输出序列, 计算公式如下:

$$f(n) = f1(n) + V_n \cdot f2(n) = f1(n) \cdot [1 + f2(n)] \quad (5)$$

通过噪声功能控制模块后, 即能模拟合并单元输出含有噪声的报文, 实现数字化电能表输入噪声测试。

### 3.2 检测平台

从图 6 可以看到检测平台包含了脉冲采集及计时模块与误差计算模块。

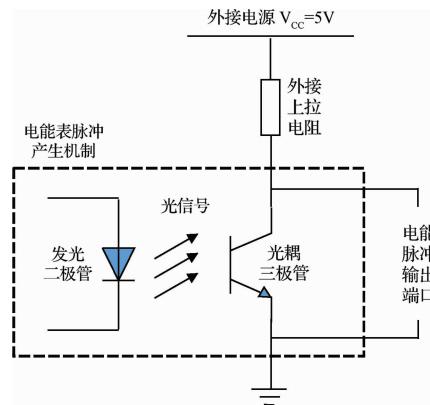

#### 1) 脉冲采集及计时模块

数字化电能表输出的电能脉冲的脉宽为  $80 \pm 5$  ms, 脉冲采集模块选取了实时性高的 FPGA 芯片实现, 利用 Verilog 硬件编程语言编写采集程序, 采集误差约为单行语句执行时间, 平台在设计时采用的是 50 MHz 的晶振, 并在 FPGA 内部将频率倍频为 150 MHz<sup>[16-18]</sup>, 语句执行时间为 ns 级, 数字电能表输出的脉冲时间间隔为 s 级, 脉冲宽度为 ms 级, 可以忽略脉冲采集带来的误差, 保证脉冲采集的高准确性, FPGA 将采集的脉冲时间通过串口传送到上位机进行误差计算。需要注意的是由于数字化电能表脉冲输出接口采用的是空接的光耦三极管<sup>[19]</sup>, 脉冲采集模块需要设置上拉电阻, 如图 8 所示。脉冲采集实现过程较为简单, 不再做过多介绍。

图 8 数字化电能表脉冲采样硬件接口设计

#### 2) 误差计算模块

误差计算模块是计算被检数字化电能表电能计量误差的部分, 上位机程序利用数字电能表脉冲常数及采集到的两个或多个脉冲之间间隔时间  $t$  及脉冲数量  $n$  计算出被检数字化电能表计量的电量  $E_1$ , 同时读取此时间段内, 标准数字功率源输出的电能量  $E_2$ , 通过对比  $E_1$ 、 $E_2$  之间的差异, 即能实现数字电能表的误差检测。被检数字化电能表的电能量  $E_1$  及误差  $\epsilon$  计算公式如下:

$$\begin{cases} E_1 = P_1 \cdot t = \frac{3.6 \times 10^6 \cdot n}{C} \\ \epsilon = \frac{E_1 - E_2}{E_2} \times 100\% \end{cases} \quad (6)$$

式中:  $C$  为数字化电能表脉冲常数, imp/kWh。 $t$  为采集的电能脉冲时间, s。 $P_1$  为被检表的有功功率, W。 $n$  为  $t$  时间段内采集到的电能脉冲数。

### 4 系统实施

为了验证检测系统的可行性及准确性, 一方面系统经由中国计量科学研究院溯源, 限于中国计量科学研究院的条件, 标准数字功率源噪声输出功能未进行溯源, 因此, 对数字功率源输出的噪声信号进行了单独分析; 另一方面利用该检测系统对通过国家标准检测的国内 3 个主流厂家的数字化电能表的进行了误差测试; 最后将测试过的数字化电能表进行了工程应用研究。

#### 1) 中国计量科学研究院溯源结果

中国计量科学研究院对该系统的检测结果表明, 标准数字功率源输出正余弦波时, 检测系统的误差为 0, 输出频率偏差时系统的最大误差为 0.001%, 最小误差为 0, 不确定度为 0.01% ( $k=2$ ), 实际上研究的检测系统误差更小, 因中国计量科学研究院选择的检测设备准确度等级/不确定度为 0.01% ( $k=2$ ), 导致检测误差为  $10^{-5}$  数量级。

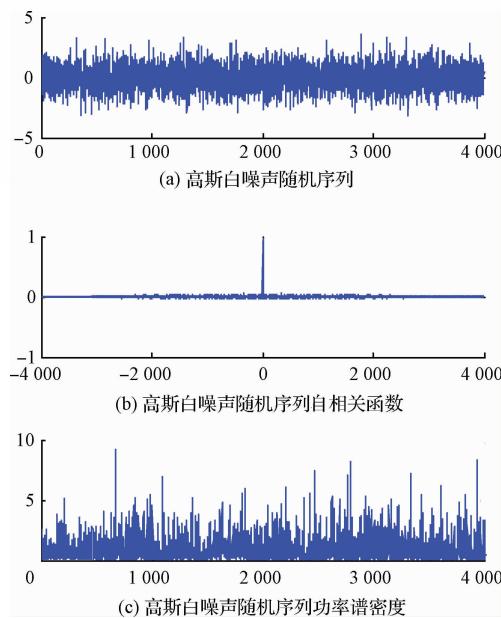

系统输出含噪声的信号验证时, 将标准数字功率源输出的含有高斯白噪声的报文进行解包, 并利用高通滤波器滤除报文中的基波信号和谐波信号成份, 留下高斯白噪声序列, 取  $N=4000$  个随机序列噪声点进行分析。 $N$  点随机序列的自相关函数  $R_x(m)$  的数学表达式为:

$$R_x(m) = \frac{1}{N} \sum_{n=0}^{N-1} X_N(n) X_N(n+m) \quad (7)$$

式中:  $X_N$  为  $N$  个序列的变量表达式,  $m=0, 1, \dots, N-1$ 。对  $R_x(m)$  进行 DFT 可得到自相关函数的功率谱  $S_x(f)$  的数学表达式为:

$$S_x(f) = \sum_{m=-(N-1)}^{N-1} R_N(m) e^{-j\omega m} \quad (8)$$

式中:  $\omega=2\pi f$ , 利用 MATLAB 软件对高通滤波器滤波后得到的  $N$  个高斯随机序列点的自相关函数及功率谱进行分析, 如图 9 所示。

从图 9 可以看到, 高斯序列的自相关函数在  $m=0$  时的值为 1, 其他接方都近似为 0, 说明该随机序列是相互独

图 9 高斯白噪声序列及自相关函数和功率谱

立的,且功率谱比较均匀,可以认为该随机序列是白色的,证明了高斯白噪声符合设计要求。

### 2) 数字化电能表测试结果

利用研究的检测系统对通过国家标准检测的国内3个主流厂家的0.2 s级的数字化电能表进行了误差测试,测试过程如图10所示。

图 10 检测系统测试

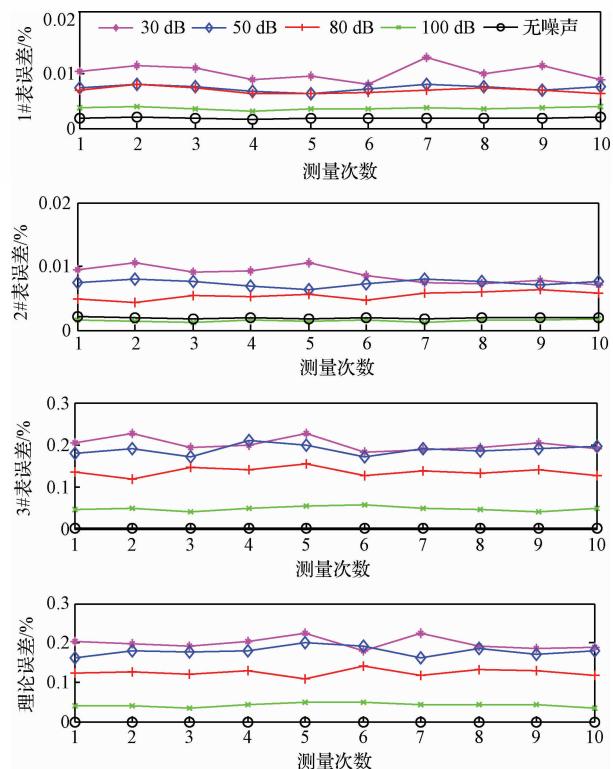

测试结果表明在基波、谐波、频率偏差条件下3个厂家数字化电能表的误差均很小,将不再过多分析。在输入电压/电流为额定值,功率为1.0时,取数字化电能表在不同信噪比条件下的误差与无噪声时误差比对的结果如图11所示,取10次测量值。

图11中测试条件参照电子式电流互感器(electronic current transformer, ECT)国家标准中规定的ECT输出的最小信噪比30 dB,信噪比变化范围为30~100 dB,测试结果显示3块数字化电能表在无噪声输入条件下,误差接近0,在添加噪声输入条件下,相比较无噪声输入时误差明显增大,说明噪声会对数字化电能表计量准确性产生明显影响,信噪比为30 dB时,3#表的误差超过0.2%,超出其准确度等级允许范围。

图 11 数字化电能表误差测试

利用MATLAB仿真软件,对输出报文数据直接进行电能量计算,发现理论误差与3#表的误差曲线相近。在输出报文数据后边添加低通滤波器后计算电能量,发现其误差与1#、2#表误差曲线相近,说明3#数字化电能表在软件算法上未设计数据滤波算法,导致误差超差,也表明了在噪声条件下对数字化电能表入网运行前进行测试的必要性,以及建立相关噪声测试项目的重要性。

### 3) 工程应用研究结果

工程应用过程中将2)中通过国家标准检测的数字化电能表应用于贵州省某110 kV数字化变电站进行长期误差监测,1个月至5个月的长期误差监测结果如表3所示。

表 3 数字化电能表长期计量误差

| 时间/月 | 数字化电能表误差/% |       |       |

|------|------------|-------|-------|

|      | 1#         | 2#    | 3#    |

| 1    | 0.083      | 0.096 | 0.224 |

| 2    | 0.112      | 0.135 | 0.323 |

| 3    | 0.096      | 0.126 | 0.263 |

| 4    | 0.115      | 0.098 | 0.287 |

| 5    | 0.127      | 0.118 | 0.361 |

从表3可以看到,输入噪声条件下误差较小的1#、2#数字化电能表的长期误差明显小于3#数字化电能表,1#、2#数字化电能表的长期误差均在其准确度等级允许范围内,而噪声条件下误差测试超差的3#数字化电能表受现场噪声影响较为严重,导致其长期计量失准。

## 5 结 论

本文从数字化电能表与电子式电能表结构差异性着手,提出应针对数字化电能表增加输入噪声测试项目,研究了一种含噪声测试的数字化电能表计量性能检测系统,该系统在现有数字化电能表检测系统的基础上进行了优化和改进,提出了一种基于M序列的Box-Muller变换高斯白噪声产生方法模拟电子式互感器A/D采样过程中叠加噪声的情况,用于数字化电能表输入噪声测试,通过对已通过国家标准检测的3个不同厂家0.2s级数字化电能表的输入噪声实验室测试及工程应用研究发现:通过国家标准检测的数字化电能表,噪声条件下,误差明显增大,尤其是在噪声条件下误差超过其准确度等级范围的3#数字化电能表现场运行过程中长期计量失准。通过本文的研究可以得到以下结论:1)输入噪声对数字化电能表计量准确性影响较为严重,数字化电能表入网运行前应增加输入噪声测试,保证入网运行的准确性和可靠性;2)本文研究的检测系统具有很高的实用值,提出的数字化电能表输入噪声测试方法能有效的对数字化电能表进行误差测试。当然,研究也存在一定的不足,限于中国计量科学研究院的检测条件,检测系统的噪声测试功能仅进行了仿真验证,尚未进行溯源,这也是下一步需要进一步展开的研究工作。

## 参 考 文 献

- [1] 廉小亲,白莉萍,金亮.电子式三相多功能电能表设计[J].仪器仪表学报,2005,26(8):287-295.

- [2] ZHANG Y H, ZHANG S Y, ZHENG J, et al. Design of single phase electronic anti-steal watt-hour based on AD7751[C]. Proceeding of 8th International Symposium on Test Measure, 2009: 1345-1348.

- [3] 艾兵,肖勇,李福超,等.基于IEC 61850通信协议的新型数字化标准电能表[J].电测与仪表,2014,51(17):1-5.

- [4] 唐毅,江波,李红斌,等.数字电能计量系统检定方法综述[J].电工技术学报,2013,28(2):372-377.

- [5] GB/T 20840.8-2007,电子式电流互感器[S]. 2007.

- [6] 陈晶.高效IEC61850-9-2数据报文发生器的设计与实现[J].通讯世界,2015(2):226-228.

- [7] 陆丰杰,申屠洁群,张佳学,等.基于IEC 61850协议的数字化电能表校验装置的研发与设计[J].电测与仪表,2015,52(6):49-55.

- [8] 孙卫明,林国营. IEC 61850协议电能表的校验方法研究[J].电测与仪表,2010,42(7A):13-16.

- [9] 袁辉,尧冬梅,张朝军.数字电能表的校验方法研究[J].中国测试,2012,38(6):20-23.

- [10] 张黎,蔡亮.基于Labview的虚拟信号发生器的设计与实现[J].国外电子测量技术,2014,33(1):82-85.

- [11] 俞富.电路噪声的成因与抑制措施[J].现代电影技术,2006(10):36-38.

- [12] 刘立超,丁凯来,林君,等.基于伪随机系统辨识的电磁法仪器标定[J].仪器仪表学报,2014,35(8):1721-1728.

- [13] 张松,张亚.基于m序列的无串扰超声波测距系统[J].电子测量技术,2015,38(10):19-24.

- [14] OBLAK M, GRUM M, Improved methods for determining the susceptibility of weights[J]. Measurements Science & Technology, 2006(17): 901-907.

- [15] LAWUNMI D. A theoretical analysis of exponentially decaying time series[J]. Measurements Science & Technology, 1997, 8(7): 703-706.

- [16] 张松,李筠.FPGA的模块化设计方法[J].电子测量与仪器学报,2014,28(5):560-565.

- [17] 王永伟,刘岩俊.嵌入式网络控制系统设计与实现[J].国外电子测量技术,2014,33(9):50-53.

- [18] YANG B F, LIU Y Y, LU Y, et al. Research of optical rainfall sensor based on CCD linear array[J]. Instrumentation, 2015, 2(3): 27-34.

- [19] 蓝永林.交流电能计量[M].北京:中国质检出版社,2011:76-93.

## 作 者 简 介

徐宏伟,1985年出生,硕士,工程师,主要从事电能计量技术研究。

E-mail:275853249@qq.com

魏伟(通讯作者),1989年出生,博士研究生,主要从事电气信息检测技术、智能电网和智能变电站二次设备的研究。

E-mail:1036243440@qq.com

张秋雁,1965年出生,本科,高级工程师,主要从事电能计量和数字化变电站技术研究。

E-mail:1072710113@qq.com

陈建国,1971年出生,工程硕士,高级工程师,现从事电能计量专业管理工作。

李红斌,1967年出生,博导,教授,从事电气信息检测技术和智能变电站二次设备的研究。